### **Combinational Circuits**

Dr Anjan Kumar Chandra Department of Physics Ramakrishna Mission Vivekananda Centenary College

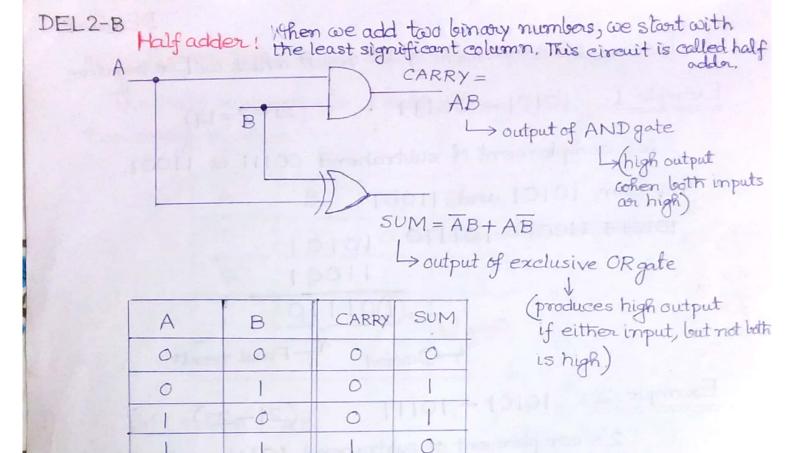

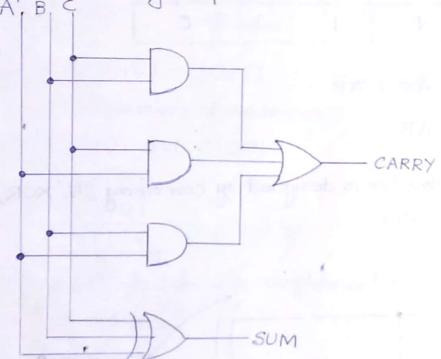

#### FULL ADDER

For higher order columns, we have to use Full Adder (a logic circuit that can add 3 bits at a time)

| A | В | C | CARRY | SUM        |

|---|---|---|-------|------------|

| 0 | 0 | 0 | 0     | 0          |

| 0 | 0 |   | 0     | - CTC      |

| 0 |   | 0 | 0     | Lobbi      |

| 0 |   |   |       | 0          |

| 1 | 0 | 0 | 0     | The second |

|   | 0 |   | blass | 0          |

| 1 | 1 | 0 | 1     | 0          |

| 1 | 1 | 1 | 1     | 1          |

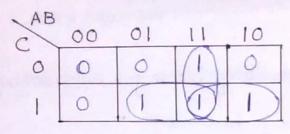

Casery = AB+BC+AC

| AB | 00 | 01 | 11 | 10   |

|----|----|----|----|------|

| 0  | 0  | -1 | 0  | al s |

| 1  | 1  | 0  | 1  | 0    |

SUM = A B B C

Carry is high when two or more of the ABC inputs are high,

When an odd number of high ABC inputs drives the exclusive OR-gate, it produces a high output.

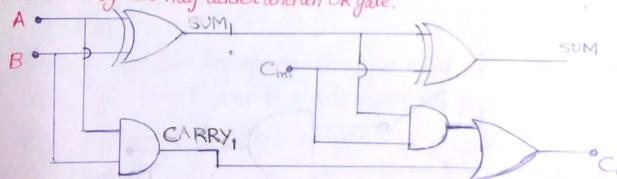

Full adder by two half adder and an OR gate.

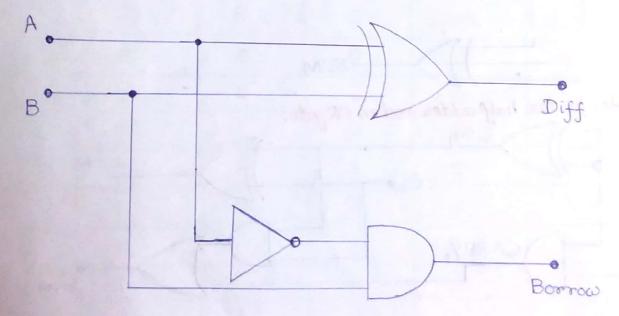

### Half Subtractor:

The half subtractor is a body building block for subtracting two binary numbers.

| A | B | Diff | Βοννοω |

|---|---|------|--------|

| 0 | 0 | 0    | 0      |

| 0 | 1 |      | 1      |

|   | 0 |      | 0      |

|   | l | 0    | 0      |

The half subtractor is designed by combining the 'XOR', 'AND' and 'NOT' gates.

#### Circuit

#### Full Subtractor

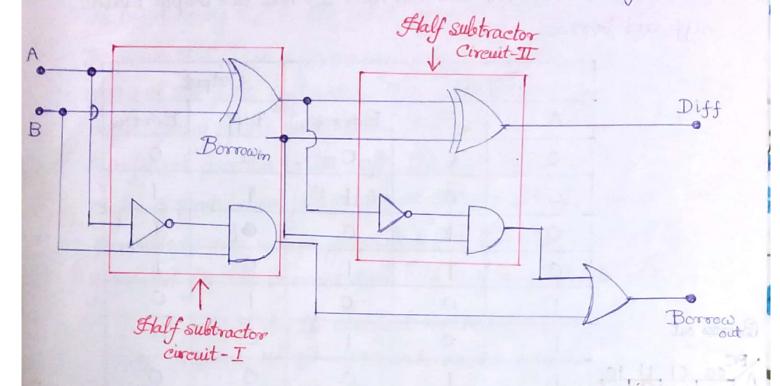

This is used to subtract three 1-bit numbers A, B and C, which minuend, subtrahend and borrow. It has two output states, diff and borrow.

| diff and be   | 1000.              | STATE AND THE |              |          |                                                               |  |

|---------------|--------------------|---------------|--------------|----------|---------------------------------------------------------------|--|

|               | Inputs             |               |              | Outpu    | t                                                             |  |

| Haran .       | A                  |               | B Borrowin   |          | Borrow                                                        |  |

|               | 0                  | 0             | 0            | 0        | 0                                                             |  |

| The Paris     | 0                  | 0             | 1            | 1        |                                                               |  |

|               | 0                  |               | 0            | @1       | 31                                                            |  |

|               | 0                  |               | 1            | 0        |                                                               |  |

|               | 1                  | 0             | 0            | 1        | 0                                                             |  |

| Borrow out    |                    | 0             |              | 0        | 0                                                             |  |

| AC00 01 11 10 |                    | 1             | 0            | 0        | 0                                                             |  |

| 0 0 1 0       | 1                  |               | bardilat \   | attle p  | and tid - in                                                  |  |

| BCim          | lf-<br>tractor Bor | Circ          | ractor Borro | A OR Gat | e > Borro                                                     |  |

| There are ta  | oo half adde       | er circuits   | that are     | romoined | Out (ABB)C+AE The Full subtraction using the ORgo two outputs |  |

|               |                    |               |              |          | stractor will l                                               |  |

of the first input of the second half subtractor.

The borrowin" will be the second input of the second half subtractor.

The second half subtractor will again provide "Diff" and "Borrow".

The final outcome of the Full subtractor circuit is the "Diff" bit.

Scanned by CamScanner

To find the final "Borrow" output, we provide the "Borrow" of the first and the second subtractor into the "OR" gate.

4-bit binary Adder/Subtractor

A binary Adder-Subtractor is a special type of circuit that is used to perform both operations, i.e. Addition and Subtraction.

We will take two 4-bit binary numbers and B for the operation.

A X -> POXIX2X3 AOAIA2A3

This circuit is a combination of 4 Full-adder, which is able to perform the addition and subtraction of 4-bit binary numbers, The control line determines whether the operation being performed is either subtraction or addition.

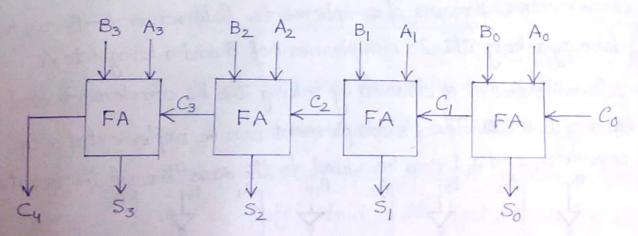

## Binary Adder

of two binary numbers. It can be constructed with full adders connected in cascade, with the output carry from each full adder connected to the input carry of the next full adder in the chain.

Addition of n-bit numbers requires a chain of n full adders. The input carry to the least significant position is fixed at 0. The

The augend bits of A and the addend bits of B are designated by subscript numbers from right to left, with subscript 0 denoting the least significant bit.

| 3 | 2           |     | 0     |         |           |

|---|-------------|-----|-------|---------|-----------|

| 0 | 1           |     | 0     | <       | $-C_i$    |

| 1 | 0           | 1   | 1     | <       | -Ai       |

| 0 | 0           | de  | 1     | <       | - Bi      |

| 1 | 1           | 1   | 0     | 4       | -Si       |

| 0 | 0           | 1   | 1     | <       | -Ci+1     |

|   | 3 0 1 0 1 0 | 0 1 | 0 1 1 | 0 1 1 0 | 0 1 1 0 0 |

Fig. shows the inter-connection of four full adder (FA) circuits to provide a four-bit binary ripply carry adder. The carries are connected in a chain through the full adders. The Soutputs generate the required sum bits.

In our example, we have considered two binary numbers, A = 1011 and B = 0011

The input carry Co in the least significant position must be 0.

The value of  $C_{i+1}$  in a given significant position is the output carry of the i-th full adder. This value is transferred into the input carry of the full adder that adds the bits one higher significant position to the left. The sum bits are thus generated as for a particular full adder as soon as the corresponding previous carry bit is generated. All the carries must be generated for the correct sum bits to appear at the outputs.

In general by the classical method it would require a truth lable with  $2^9 = 512$  entries, since there are nine inputs to the circuit. By using an iterative method of cascading a standard function, it is possible to obtain a simple and straight forward implementation.

# Binary Subtractor

FA

The subtraction of unsigned binary numbers can be done most conveniently by means of complements. Subtraction A-B can be done by taking the 2's complement of B and adding it to A.

2's complement is obtained by taking the 1's complement and adding 1, toothe The 1's complement can be implemented with inverters, and a 1 can be added to the sum through the input cavoy.

By A3 B21 A2 B11 A1 B01 A0

FA

Let us take the example:

$$A \rightarrow 1011 (11)_{10}$$

$B \rightarrow 0011 (3)_{10}$

15265 complement of B is \$100 Now add 1011 and 01100

Here Co=1 151219160 with Co=1

1100

Cy is the final carry which is ignored The final result is 1000 (8),

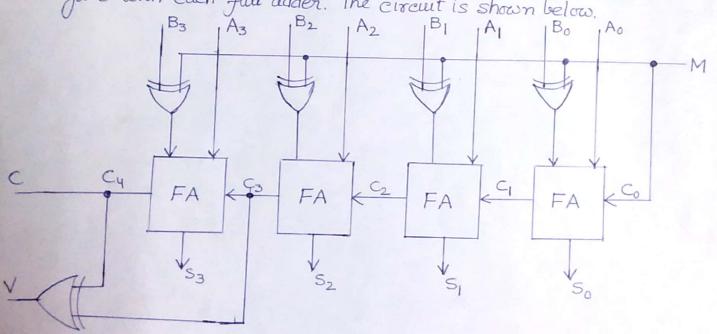

## Binary adder - subtractor :

The addition and subtraction operations can be combined into one circuit with one common binary adder by including an exclusive-OR gate with each full adder. The circuit is shown below.

The mode input M controls the operation (adder/subtractor).

$M=0 \longrightarrow adder$

=1 -> subtractor

Each exclusive-OR gate receives input M and one of the inputs of B. When M=0,  $B\oplus O=B$   $\Rightarrow$  Full adders receive the value of B, and the circuit input cavey is 0 and the circuit performs A plus B.

#### DEL4-B

When M=1,  $B \oplus 1 = \overline{B}$  and  $C_0 = 1$

As the B inputs one complemented and the input carry is 1, the circuit performs the operation "A plus 2's complement of B". (The exclusive-OR with output V is for detecting an overflow).